## **Design of Robust CAN-FD Networks**

An automated Model based Design Flow

**Federico Pereira**

## Design flow introduction

**Topology simulation**

Validation criteria

Need for automatization

Conclusion

www.cs-group.de communication & systems group

## Design flow introduction

**Topology simulation**

Validation criteria

Need for automatization

Conclusion

www.cs-group.de communication & systems group

**C & S**

. 🏓 .

### Why should I simulate?

- Constant increase of quality and performance in todays requirements within in-vehicle networks (IVN) systems

- Quality assurance

- Further analysis compared to laboratory test

- Total cost reduction

We consider simulation as the most important phase in validating a modern topology

## **Design flow introduction (2/2)**

## 3 main steps are distinguished in this kind of design flow:

- Topology simulation

- Virtual network prototype

- Laboratory measurements

- Real network test

- Verification

- Comparison between the virtual measurements and

real measurements

#### Design flow introduction

# **Topology simulation**

Validation criteria

Need for automatization

Conclusion

www.cs-group.de communication & systems group

**C & S**

. 🏓 . .

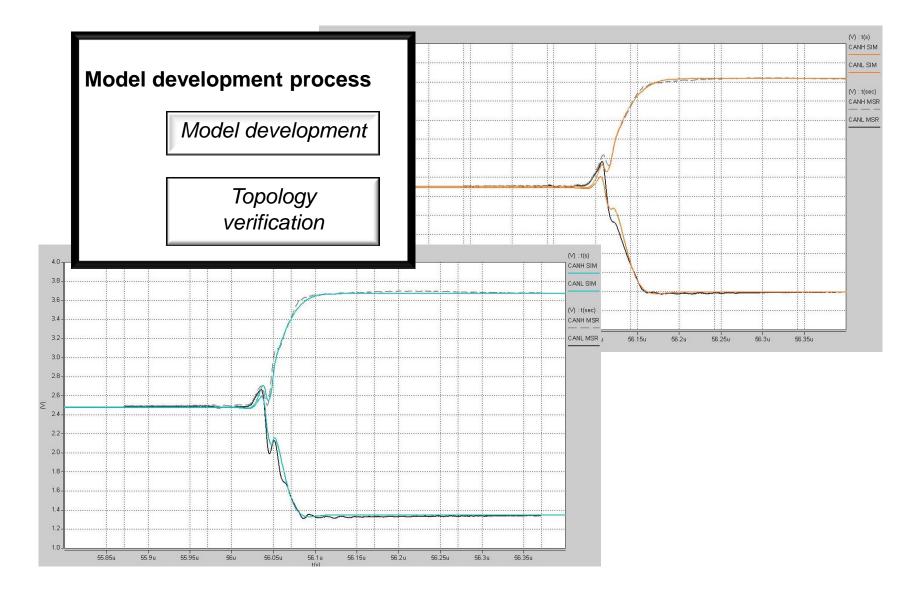

| Model development process |                          |  |  |

|---------------------------|--------------------------|--|--|

|                           | Model development        |  |  |

|                           | Topology<br>verification |  |  |

www.cs-group.de communication & systems group

8

| Model development process |                                              |

|---------------------------|----------------------------------------------|

| Model development         |                                              |

| Topology<br>verification  | #8                                           |

|                           | 8,1m                                         |

|                           | (#7)<br>7,1m<br>(#1)<br>1,2m<br>(#2)<br>(#2) |

|                           | (#6)-5,9m-3,1m-(#3)                          |

|                           | (#5) <sup>5,2m</sup><br>4,5m                 |

|                           | 4,511                                        |

www.cs-group.de communication & systems group

www.cs-group.de communication & systems group

10

**C & S**

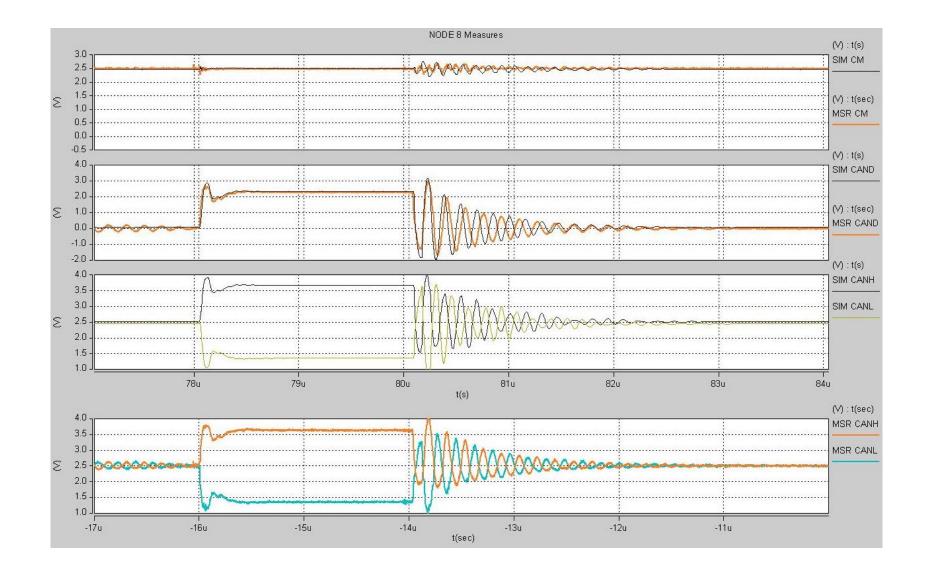

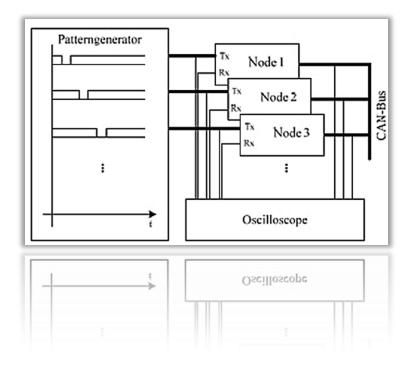

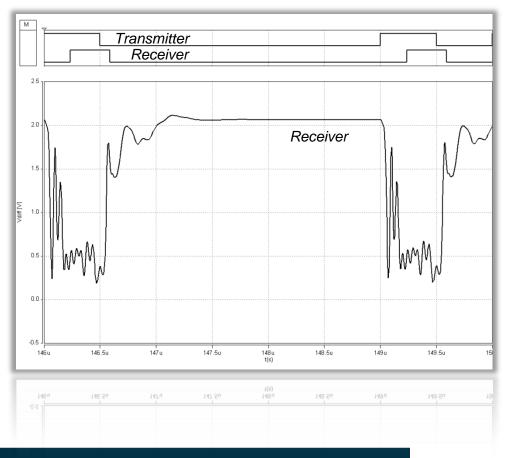

#### **Round robin communication**

[Pattern generator] creates a digital input signal to the TXD pin of each transceiver with the required data rate

• • • C & S

#### Pattern applied to each node

A typical scenario is used when 5 dominant bits are followed by a unique recessive bit

This combination assures the worst condition after charging/discharging the capacitances

#### Design flow introduction

Topology simulation

## Validation criteria

Need for automatization

Conclusion

www.cs-group.de communication & systems group

**C & S**

. 🏓 .

#### **Clock tolerance**

Though this rules concentrate on the bit timing only and do not involve topology effects, clock settings must respect the rules defined in *"Robustness of a CAN FD Bus System – About Oscillator Tolerance and Edge Deviations"* by Dr. Arthur Mutter

In special, we consider the clock tolerance as df:

$$(1-df) < \frac{f_{CAN}}{f_{nom}} < (1+df)$$

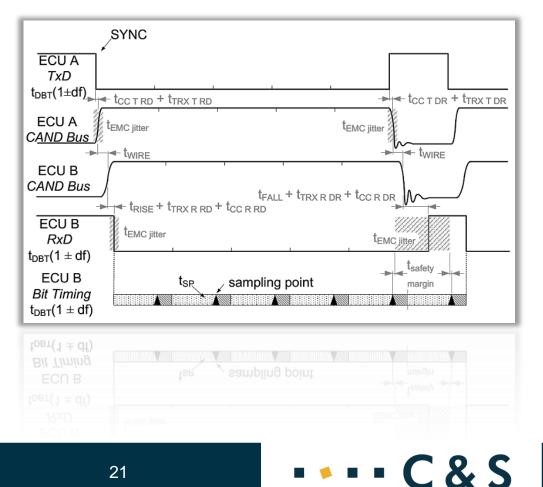

#### Safe sampling

Focused on the different propagation delays for a dominant to recessive edge and vice versa.

"The symmetry becomes more important with the increasing of the baud rate"

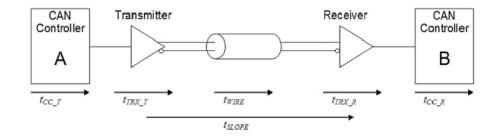

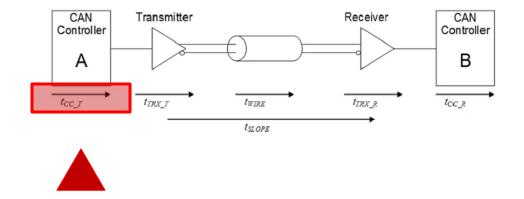

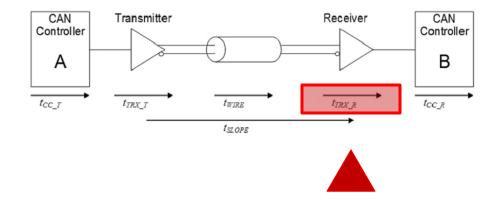

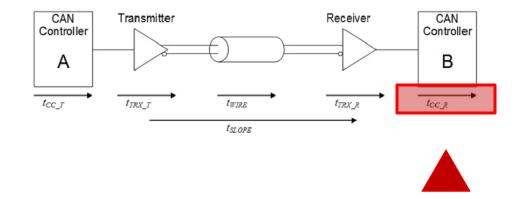

#### $-t_{CC_T}$ CAN controller delay on the transmitter side

www.cs-group.de communication & systems group

•••• C & S

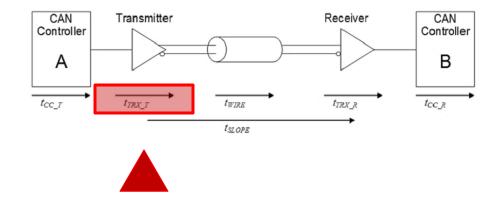

$-t_{CC_T}$ CAN controller delay on the transmitter side $-t_{TRX_T}$ Transceiver delay on the transmitter side

•••• C & S

- CAN controller delay on the transmitter side  $-t_{CC_T}$

- Transceiver delay on the transmitter side  $-t_{TRX T}$

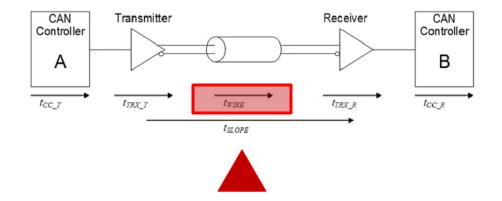

- $-t_{WIRE}$

- Wire delays

**C & S**

- $-t_{CC_T}$  CAN controller delay on the transmitter side

- $-t_{TRX_T}$  Transceiver delay on the transmitter side

- $-t_{WIRE}$  Wire delays

- $-t_{TRX_R}$  Transceiver delay on the receiver side

- $-t_{CC_T}$  CAN controller delay on the transmitter side

- $-t_{TRX_T}$  Transceiver delay on the transmitter side

- $-t_{WIRE}$  Wire delays

- $-t_{TRX_R}$  Transceiver delay on the receiver side

- $-t_{CC_R}$  CAN controller delay on the receiver side

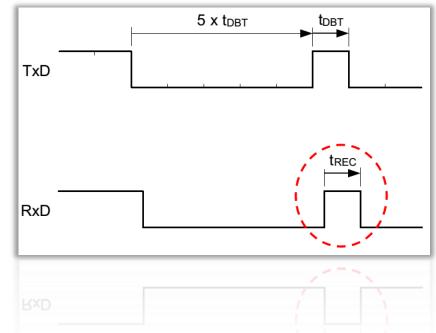

#### We consider $t_{REC}$ as:

$$t_{REC} = t_{BIT_D} - \left(t_{TRX\_T_{DR}} - t_{TRX\_T_{RD}}\right) - \left(t_{TRX\_R_{DR}} - t_{TRX\_R_{RD}}\right) - \left(t_{DR} - t_{RD}\right)$$

- $t_{REC}$ : Measured recessive time

- $t_{BIT_p}$ : The time of a bit in data phase

- TRX: Transceiver delay

- **T**: Transmitting side

- **R**: Receiving side

- **DR**: Dominant to recessive edge  $(t_{WIRE} + t_{FALL})$

- **RD**: Recessive to dominant edge

$(t_{WIRE} + t_{RISE})$

A safety margin **before** and **after** the sampling point shall be considered

### Sampling point - 1<sup>st</sup> Safety margin

Can be considered as the minimal distance between the sample point and the received edge at the beginning of the ideal bit and

#### Sampling point - 2<sup>nd</sup> Safety margin

Minimal distance between the received edge at the end of the ideal bit and the sample point

#### For Robustness, following inequalities must be satisfied

- Supposing that node A is **faster** than node B

$t_{REC} < t_{BIT_D} + t_{SP(df_{B+})} + t_{CC} - t_{CLK} - t_{SM}$

- Supposing that node A is **slower** than node B  $t_{REC} > t_{SP(df_{B-})} + t_{CC} + t_{CLK} + t_{SM}$

- $t_{BIT_D}$ : The time of a bit in data phase

- $t_{SM}$ : Safety margin including factors as EMC jitter

- $t_{SP}$ : Sample point time within a bit

- $df_{B+/-}$ : Index to indicate that the frequency is deviated due to clock deviation

- $t_{CC}$ : Controller processing time

- $t_{CLK}$ : Clock tolerance influence

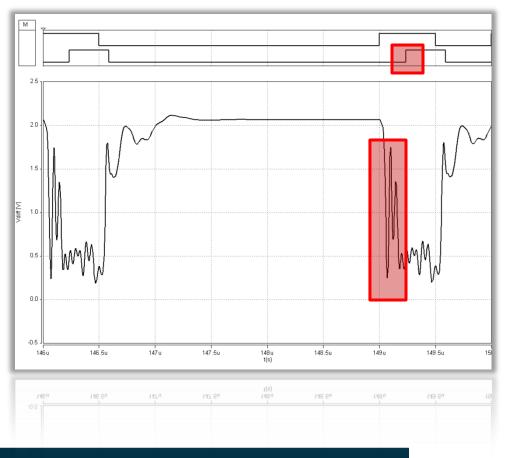

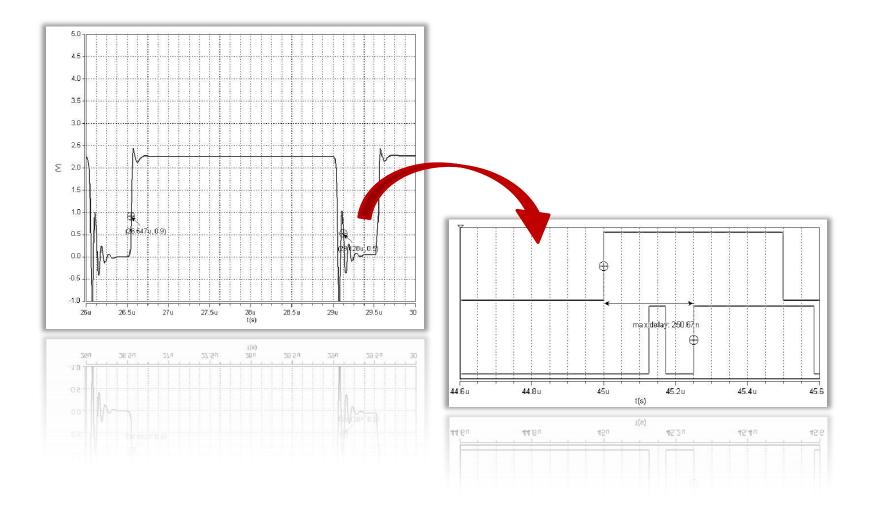

### Validation criteria – Example with $t_{REC}$ too small

Bit time = 500 [ns]

www.cs-group.de communication & systems group

24

**C & S**

🔰 🔳 🔳

## Validation criteria – Example with $t_{REC}$ too small

Bit time = 500 [ns]

**Measured value** = 179 [ns], thus the minimum is not satisfied.

This is reported as a **FAIL** condition for this topology. The same is applied if the recessive time results are too large.

www.cs-group.de communication & systems group

**C & S**

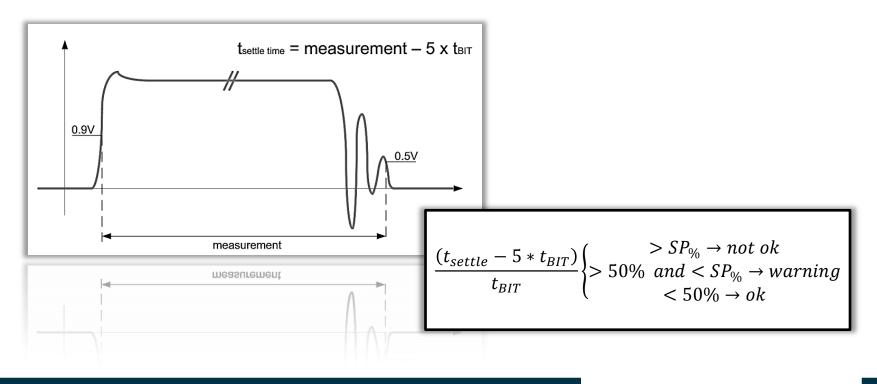

### Validation criteria – Settle time

#### Settle time can be measured in two different approaches

- Edge oriented measurement Falling time of the signal from the higher threshold to the lower threshold

- Bit oriented measurement Same as above but including the 5 dominant bits before changing to recessive state

www.cs-group.de communication & systems group

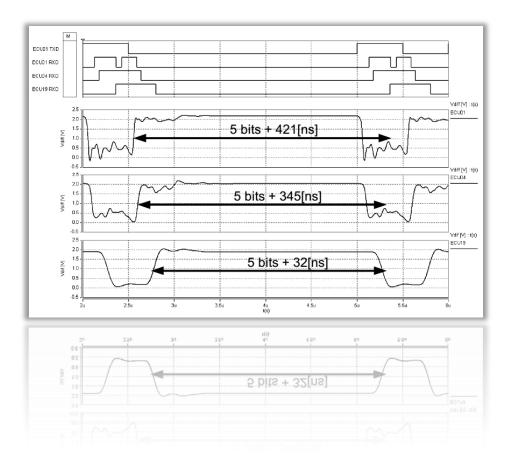

### Validation criteria – Settle time example

#### 3 different verdicts are met in this example

| Table 1: Example of simulation outputs |                   |          |             |         |

|----------------------------------------|-------------------|----------|-------------|---------|

| TX<br>node                             | RX<br>node        | Measure  | Limit       | Verdict |

| ECU <sub>1</sub>                       | ECU₁              | 421 [ns] |             | FAIL    |

| ECU <sub>1</sub>                       | ECU₄              | 345 [ns] | 400<br>[ns] | WARN.   |

| ECU <sub>1</sub>                       | ECU <sub>19</sub> | 32 [ns]  |             | PASS    |

| ECU1 | ECU <sub>19</sub> | 32 [ns] |             | PASS |

|------|-------------------|---------|-------------|------|

|      |                   |         | 400<br>[ns] |      |

www.cs-group.de communication & systems group

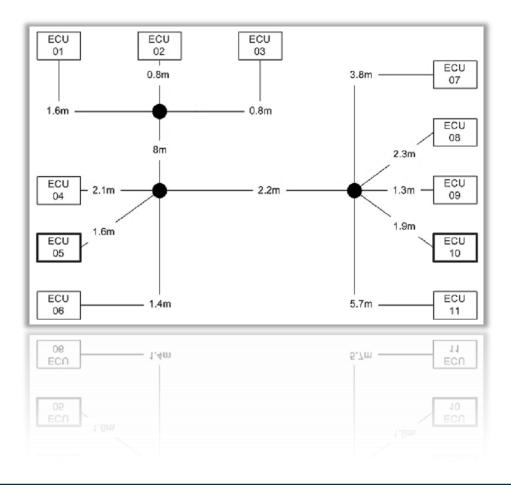

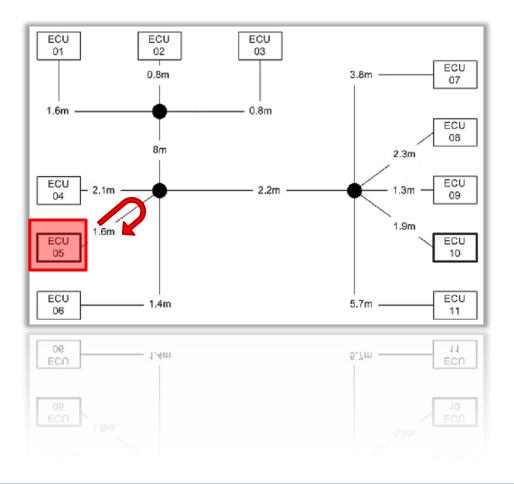

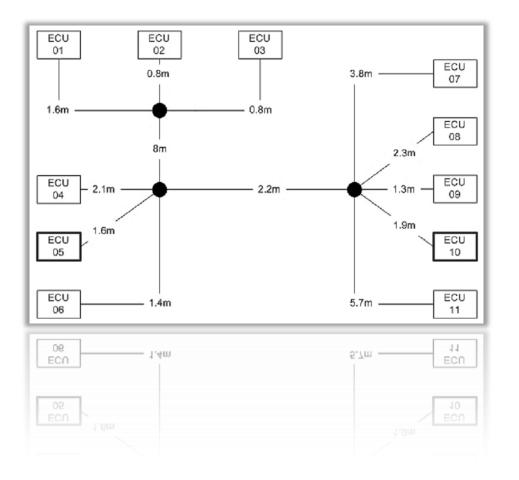

### Validation criteria – Confidence level (1/4)

### 11 Nodes, 2 of them with low resistance termination

#### **3 passive stars**

www.cs-group.de communication & systems group

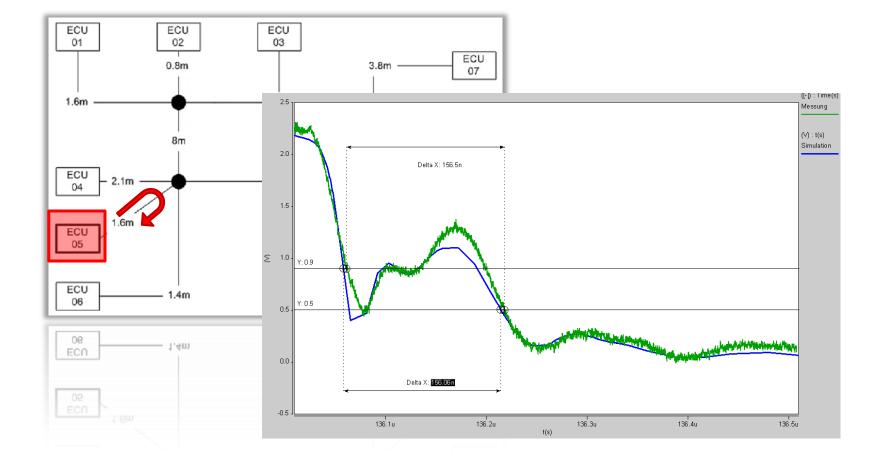

#### Settle time example

www.cs-group.de communication & systems group

### Validation criteria – Confidence level (3/4)

www.cs-group.de communication & systems group

30

### Validation criteria – Confidence level (4/4)

| Baud<br>rate [Mb/s] | Simulation        | Measurement       |

|---------------------|-------------------|-------------------|

| 0.5                 | PASS              | PASS              |

| 1                   | PASS              | PASS              |

| 2                   | PASS <sup>1</sup> | PASS <sup>1</sup> |

| 3                   | FAIL              | FAIL              |

| 4                   | FAIL              | FAIL              |

| 5                   | FAIL              | FAIL              |

| 5     | FAIL                      | FAIL |  |

|-------|---------------------------|------|--|

| 4     | FAIL                      | FAIL |  |

|       |                           |      |  |

| 1. On | 1. Only with optional TDC |      |  |

•••C&S

www.cs-group.de communication & systems group

#### Design flow introduction

## **Topology** simulation

Validation criteria

## Need for automatization

#### Conclusion

**C & S**

. 🚺 .

- Todays implementations demand automatization

- Each topology is evaluated independently

- Example:

- -

- -

- -

- -

•••• C & S

- Nowadays implementations demand automatization

- Each topology is evaluated independently

- Example:

- 11 Nodes (n=11)

- -

- -

•••• C & S

- Nowadays implementations demand automatization

- Each topology is evaluated independently

- Example:

- 11 Nodes (n=11)

- 4 edges (Transmitter/Receiver, D2R and R2D)

- Nowadays implementations demand automatization

- Each topology is evaluated independently

- Example:

- 11 Nodes (n=11)

- 4 edges (Transmitter/Receiver, D2R and R2D)

- Test at 2Mb/s and at 5Mb/s

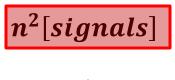

# **Need for automatization**

- Nowadays implementations demand automatization

- Each topology is evaluated independently

- Example:

- 11 Nodes (n=11)

- 4 edges (Transmitter/Receiver, D2R and R2D)

- Test at 2Mb/s and at 5Mb/s

- 3 Temperature conditions should be evaluated (high, room, low)

n<sup>2</sup>[signals].4[edges].2[freq].3[temp]

# **Need for automatization**

- Nowadays implementations demand automatization

- Each topology is evaluated independently

- Example:

- 11 Nodes (n=11)

- 4 edges (Transmitter/Receiver, D2R and R2D)

- Test at 2Mb/s and at 5Mb/s

- 3 Temperature conditions should be evaluated (high, room, low)

n<sup>2</sup>[signals].4[edges].2[freq].3[temp] = 2904 measurements!

- Nowadays implementations demand automatization

- Each topology is evaluated independently

- Example:

- 11 Nodes (n=11)

- 4 edges (Transmitter/Receiver, D2R and R2D)

- Test at 2Mb/s and at 5Mb/s

- 3 Temperature conditions should be evaluated (high, room, low)

$n^{2}[signals].4[edges].2[freq].3[temp] = 2904$  measurements!

Keep counting, we must analyze also the arbitration phase...

- Nowadays implementations demand automatization

- Each topology is evaluated independently

- Example:

- 11 Nodes (n=11)

- 4 edges (Transmitter/Receiver, D2R and R2D)

- Test at 2Mb/s and at 5Mb/s

- 3 Temperature conditions should be evaluated (high, room, low)

$n^{2}[signals]$ . 4[edges]. 2[freq]. 3[temp] = 2904 measurements! Keep counting, we must analyze also the arbitration phase...

What about the human error? Automatization gives quality as well

#### **Need for automatization**

#### What happens after measurements? Should we adjust the topology?

www.cs-group.de communication & systems group

•••C&S

#### Design flow introduction

# **Topology** simulation

Validation criteria

Need for automatization

# Conclusion

www.cs-group.de communication & systems group

**C & S**

. 🏓 . .

#### **CAN FD means higher data rate and even larger payloads**

- •

- •

- •

- •

••••C&S

www.cs-group.de communication & systems group

•

**CAN FD means higher data rate and even larger payloads**

Simulation nowadays is an excellent approach to overcome the design problems at an early stage of a vehicle development and/or newer versions of existent designs

••C&S

#### **CAN FD means higher data rate and even larger payloads**

- Simulation nowadays is an excellent approach to overcome the design problems at an early stage of a vehicle development and/or newer versions of existent designs

- The most important factor for higher frequencies is asymmetry and simulation is an excellent tool to evaluate it

#### **CAN FD means higher data rate and even larger payloads**

- Simulation nowadays is an excellent approach to overcome the design problems at an early stage of a vehicle development and/or newer versions of existent designs

- The most important factor for higher frequencies is asymmetry and simulation is an excellent tool to evaluate it

- Not only typical signals can be analyzed but those affected by tolerances and specified ranges as well

#### **CAN FD means higher data rate and even larger payloads**

- Simulation nowadays is an excellent approach to overcome the design problems at an early stage of a vehicle development and/or newer versions of existent designs

- The most important factor for higher frequencies is asymmetry and simulation is an excellent tool to evaluate it

- Not only typical signals can be analyzed but those affected by tolerances and specified ranges as well

- Automatization is what makes simulation an effective way in the Topology analysis

•

•••C&S

#### **CAN FD means higher data rate and even larger payloads**

- Simulation nowadays is an excellent approach to overcome the design problems at an early stage of a vehicle development and/or newer versions of existent designs

- The most important factor for higher frequencies is asymmetry and simulation is an excellent tool to evaluate it

- Not only typical signals can be analyzed but those affected by tolerances and specified ranges as well

- Automatization is what makes simulation an effective way in the Topology analysis

- Automatization + Simulation gives a extended focus to designers

•••C&S

# Thank you for your attention!

••••C&S

www.cs-group.de communication & systems group

49

#### What can we test for you?

#### C & S group GmbH

Am Exer 19b 38302 Wolfenbüttel Germany Tel +49 53 31 · 90 555 0 Fax +49 53 31 · 90 555 110

info@cs-group.de www.cs-group.de **Federico Pereira** f.pereira@cs-group.de