# Requirement Specification for Transceiver Simulation Models

**Transceiver Model Specification**

V 1.1

## Document history

| Version    | Datum     | Author                           | Comments                                                  |  |

|------------|-----------|----------------------------------|-----------------------------------------------------------|--|

| 0.3        | 09 / 2004 | Dietmar Ostowski (DO)            | Revised initial draft DaimlerChrysler                     |  |

| 0.4 / 0.4a | 10 / 2004 | DO /                             | Feedback VW                                               |  |

|            |           | Carsten Schanze (CS)             |                                                           |  |

| 0.4b       | 01 / 2005 | CS / DO                          | Feedback VW                                               |  |

| 0.4b/e     | 05 / 2005 | Andreas Dante (AD) / DO          | Translation of version 0.4b into English                  |  |

| 0.4c       | 02 / 2006 | CS                               | Feedback Infineon (Munich Meeting 2006-02-07)             |  |

| 0.4d       | 03 / 2006 | Harald Bayer (HB), DO            | Feedback Mr. Suermann, Philips 2005-02-07                 |  |

|            |           |                                  | Feedback Mr. Gerke, Synopsys, 2005-06-08                  |  |

| 0.4e       | 04 / 2006 | CS                               | Feedback Mr. Michenthaler, Audi                           |  |

| 0.99       | 06 / 2006 | DO / HB / CS                     | Revised Version DaimlerChrysler and VW                    |  |

| 0.99a      | 03 / 2007 | DO                               | English translation                                       |  |

| 0.99b      | 07 / 2007 | Günter Kircher (GK) /            | Layout and Contend changed according to                   |  |

|            |           | Christoph Wosnitza (CW) /        | GIFT Consortium by C&S                                    |  |

|            |           | Marko Moch (MMO)                 |                                                           |  |

| 0.99c      | 09 / 2007 | Günter Kircher (GK) /            | Changes according to review phase                         |  |

|            |           | Christoph Wosnitza (CW) /        |                                                           |  |

|            |           | Marko Moch (MMO)                 |                                                           |  |

| 0.99d      | 10 / 2007 | Günter Kircher (GK) /            | Changes according to TelCo discussion results             |  |

|            |           | Christoph Wosnitza (CW) /        |                                                           |  |

|            |           | Marko Moch (MMO)                 |                                                           |  |

| 1.0        | 01 / 2008 | Günter Kircher (GK) /            | Changes according to TelCo and Meeting discussion results |  |

|            |           | Christoph Wosnitza (CW) /        |                                                           |  |

|            |           | Marko Moch (MMO)                 |                                                           |  |

| 1.1        | 12 / 2009 | Marko Moch (MMO)                 | Changes according to 2009-09-29 and 2009-11-24 TelCo      |  |

|            | 01 / 2010 | Mounier Philippe                 | Note (6) added                                            |  |

|            | 02 / 2010 | Dietmar Ostowski<br>Harald Bayer | Modification of the first paragraph of chapter 3.6        |  |

## Contents

| Trans | ceiver Model Specification                                                                                                                                                                                         | 1                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1     | Targets                                                                                                                                                                                                            | 4                    |

| 2     | Simulation Environment                                                                                                                                                                                             |                      |

| 3     | Model Requirements 3.1 Simulator operating modes 3.2 Validity Range 3.3 Model Interfaces (Pins and Parameter) 3.4 Functionality 3.5 Model Parameterisation 3.5.1 Implementation 3.6 Levels of model implementation | 6<br>7<br>8<br>9     |

| 4     | Support Requirements 4.1 Model Documentation 4.2 Model Application 4.2.1 Test Bench 4.3 Model Maintenance 4.4 Delivery Dates                                                                                       | 13<br>13<br>13<br>14 |

| 5     | Contacts                                                                                                                                                                                                           | 15                   |

| 6     | Annex                                                                                                                                                                                                              | 16<br>16             |

# 1 Targets

In this specification the demands on the simulation models of the transceivers for vehicle networks as well as the required scope of services through the semiconductor manufacturers are described.

#### 1.1 Aim and Motivation

The simulation models of the transceivers are supposed to be used for the simulation of the physical level of vehicle networks.

The simulations should give early indications over:

- the influence of different topologies on the system operation,

- the evaluation of the functionality in case of changes to the system,

- requirements for future transceivers,

- the impact of specific limiting conditions in the automotive environment,

- the interaction of system components (e.g. the influence of additional components on transceiver functions),

- the system operation for specified "worst case scenarios" or at the system boundary.

The simulation contributes to the system reliability. Changes to the vehicle topology and the demands on components (e.g. transceivers) are avoided.

The actual specification focuses on CAN-Transceivers. The intention is to extend the specification to cover LIN also. Therefore, some parameters for LIN are already included. FlexRay is out of scope for the moment

#### 1.2 Use of the Simulation

The simulation is used for the inspection of the system operation of the communication layer of networks in standard and worst case scenarios. The simulations are performed including dynamic behaviour in the time domain. The focus is on the validation of topology, circuit influences on the signal integrity, delay times and the interactions with bus drivers.

In this context, the simulated network architecture primarily consists of the physical layer, which may optionally be extended by parts of the Medium Access Control sub layer (data link layer, please refer to the related network specification e.g. ISO 11898 / -1).

On one hand complete vehicle networks including specific constraints should be simulated, on the other hand individual system parts for investigations of basic influences are evaluated. The specific constraints include e.g.:

- different bus topologies

- system variables

- termination concepts

- EMC arrangements

- partial network use

- mixed transceiver networks

- variations of the supply voltage

- ground shift

- different transceiver states (normal mode, sleep mode, etc.)

Beside the simulation with its typical technology parameters (typical values according to data sheet), the simulation of defined worst case scenarios should also be possible. Affected values are e.g. delay times, static power consumption of the device in different states or operational modes, and signal symmetry (e.g. temporal shift of the signal edges).

## 2 Simulation Environment

The models have to be executable in the following simulation environment. The test and evaluation of the transceiver simulation models will be executed in a defined test bench. The test bench is specified in a separate document.

## 2.1 Description Languages

The following Description Language should be used for modeling:

- VHDL-AMS

- Currently the VHDL-AMS standard is not completely covered by any simulation tool available and some components are written in other languages included as "dll"-library for example. For the intervening period until full coverage of VHDL-AMS is achieved, models are delivered specifically for any of the simulation tools.

The models can be delivered as:

- clean model description source code

- precompiled library (for the simulator tool specified by the customer, see ch. 4.2)

- encrypted model description source code (encrption based on VHDL-2008)

For the model description itself, no proprietary libraries nor foreign routines are allowed.

# 3 Model Requirements

### 3.1 Simulator operating modes

The transceiver model must support following simulation types:

#### - DC Analysis (Operating Point)

The DC Analysis computes the state of the system at time 0. This analysis is the initial point for subsequent analyses.

In detail, this analysis defines the steady state of a nonlinear system at time 0. All time varying parameters and their derivates are set to 0. All dynamic elements are ignored and effectively removed from the circuit (capacitances are removed from the circuit, inductances are short circuited and time dependent sources removed). Noises and AC sources are removed too.

### Transient Analysis (Time Domain Analysis)

The Transient Analysis computes the systems behaviour as a function of time. The calculated datapoints in the time domain are time steps. The values of each time step are used for determining an initial guess at the next solution point in the simulation. The results are similar as the measurements were shown on oscilloscope.

Specific measurements are rise time, fall time, slew rate, period, frequency, duty cycle, pulse width, delay, overshoot, undershoot and settle time.

#### - Statistical Analysis (Monte Carlo)

The Monte Carlo Analysis defines statistical method for the investigation of a circuit. At this type of analysis, component parameters are randomly varied within user specified tolerance ranges. The Monte Carlo method defines a set execution runs with basic analysis types with the parameter sets being varied (e.g. Transient Analysis).

The correlation between variations of performance parameters and variations of independent component parameters are computed. These results are used to define a statistical sensitivity to determine how much the percent change in performance can be correlated with a percent change in each parameter. The parameters are randomly varied in their tolerance band.

For Monte Carlo analysis, the external transceiver model parameter shall be varied only.

#### Parameter Sweep Analysis (Vary)

This analysis uses a deterministic method to identify the impact of individual parameters on system performance by changing only one parameter at a time by a small and fixed amount. With that, the perturbation is measured to the measured performance.

The design parameters are changed by a small amount for calculating the effect of performance measure. It helps to determine and isolate components which contribute to specific unwanted measures, e.g. voltage overshoot.

## 3.2 Validity Range

The transceiver model must correspond to the behaviour described in the data sheet within the operating range limits specified in the data sheet concerning the required function scope. Guaranteed behaviors of transceiver are described in the data sheet only. In addition, a correct impedance behaviour at the bus pins is demanded in the unsupplied state ( $V_{CC} = V_{BAT} = 0 V$ ) (Reverse current paths).

The transceiver model must reproduce the behaviour specified in the valid data sheet concerning the subsequently required function scope.

In the case that the range of validity is exceeded after the simulation run, error or warning reports have to be issued by a monitoring system, which has to be implemented in the model. This monitoring system has to include the supply voltages, the inputs and outputs (voltage and current ranges at analogue pins and logical levels at digital pins), as well as other variables and selectable parameters (e.g. for the switching between typical and limit values for parameterization of temperature and  $V_{cc}$  range; see chapter 3.5). This ensures, that only plausible and valid values are used and that the simulation returns realistic results. The monitoring system has to be documented how it is implemented.

DC Analysis: The error reports shall occur at the end of the analysis only.

Transient Analysis: The error reports shall occur at the end of a time step.

## 3.3 Model Interfaces (Pins and Parameter)

The real pins of single chip transceiver including all model variations shall be implemented according to which level of model implementation is required by the customer, see chapter 3.6. Implementations of System Basis Chips have to conform the functionally ambit described in chapter 3.4.

Parameterization (cp. chapter 3.5) and model variation might request additional pins and parameters as input to the model. The parameter must be described and their ranges must be controlled in the simulation model (cp. Chapter 3.2 and 4.1).

| Interface Pins / Parameters              | Example                                                                                                  | Requirements (according to Data sheet)                                                                                                                                                                                                                                                                                                                                                                              | Implementation Option                                                                                                                                               |

|------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Supply                             | $\begin{array}{c} \text{GND, V}_{\text{CC}}, \\ \text{V}_{\text{bat}}, \text{V}_{\text{io}} \end{array}$ | analogue interface implementation     voltages, currents                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>VCC, GND: mandatory regardless of the model level</li> <li>all others: optional regarding the model level and their presense at the real device</li> </ul> |

| Bus Interface                            | CANH,<br>CANL,<br>SPLIT                                                                                  | <ul> <li>analogue interface implementation</li> <li>correct currents, power, impedances (also at VCC = 0 V)</li> <li>representation of correct impedance for completely un-powered (GND = Vcc) Transceiver</li> <li>correct short circuit behaviour, signal integrity, symmetry, slew rate, delays, filter, thresholds, internal termination</li> <li>validity in all operation modes of the transceiver</li> </ul> | <ul> <li>CANH, CANL: mandatory regardless of the model level</li> <li>SPLIT: optional by its presence at the real device</li> </ul>                                 |

| Communication<br>Controller<br>Interface | TxD, RxD                                                                                                 | <ul> <li>digital interface implementation</li> <li>correct delays</li> <li>analogue interface implementation</li> <li>correct currents, impedances, delays, filter, thresholds, signal integrity, slew rate</li> </ul>                                                                                                                                                                                              | TxD, RxD: mandatory regardless of the model level digital / analogue implementation regarding the model level                                                       |

| Host Control<br>Interface                | OPM0,<br>OPM1,<br>WAKE,<br>ERR                                                                           | <ul> <li>digital interface implementation</li> <li>logic behaviour</li> <li>analogue interface implementation with filters,</li> <li>threshold voltages, impedances</li> </ul>                                                                                                                                                                                                                                      | All: optional regarding the model level digital / analogue implementation regarding the model level                                                                 |

| Voltage<br>Regulator<br>Control          | INH                                                                                                      | <ul> <li>analogue interface implementation</li> <li>impedance of output pins (output capacitance, current driving capability)</li> <li>output voltage (no load) dependent on supply voltage</li> </ul>                                                                                                                                                                                                              | INH: optional regarding the model level and its presense at the real device                                                                                         |

| Parameters                               | TEMP                                                                                                     | <ul><li>parameter cp. chapter 3.5</li><li>description for the high/low effects</li></ul>                                                                                                                                                                                                                                                                                                                            | - TEMP: mandatory                                                                                                                                                   |

Table 1: Model interface implementation requirements

Requirements for all existing pins (excepting V<sub>CC</sub>):

- Validity of model behaviour according to the voltage ranges denoted in the data sheet,

Signal- and parameter monitoring (valid range), error and warning reports have to be implemented e.g. if passing operational limits (Ch. 3.4, 4.1).

Requirements for V<sub>CC</sub> pin:

- V<sub>CC</sub> fixed to nominal voltage or 0V,

- Validity of model behaviour according to typical and unpowered condition denoted in the data sheet,

Global parameters (High / Low Temp) to force the model into the worst case corners including the  $V_{CC}$  influence. (cp. chapter 3.5)

## 3.4 Functionality

Besides the transmit and receive functionality, transceiver devices often provide additional functions for low power management, wake-up, diagnosis etc. Table 2 gives an overview of common functions and describes to what extent the function shall be modelled. The set of functions to be covered by a model depends on the level of simulation model (cp. chapter 3.5).

| Function             | Modelling reuirements                               |

|----------------------|-----------------------------------------------------|

| Transmitter function | Propagation delay TXD to bus                        |

|                      | Differential bus output amplitude                   |

|                      | - Differential bus slope                            |

|                      | - GND offset                                        |

| Receiver function    | Propagation delay bus to RXD                        |

|                      | - Receiver thresholds                               |

|                      | - GND offset                                        |

| Bus biasing          | Level of bus biasing (nom. value)                   |

|                      | - Impedance of bus biasing                          |

|                      | Differential input resistance                       |

|                      | Common mode input resistance                        |

| Operating modes      | Current consumption on supply pins in all modes     |

|                      | Signalling on output pins                           |

|                      | Impedance behaviour on bus pins for all modes       |

| Bus wake-up          | Wake-up receiver timings (e.g. delays)              |

|                      | Wake-up receiver thresholds                         |

| Local wake-up        | - Input threshold                                   |

|                      | - Timings (delay, filter etc.)                      |

| Diagnosis            | Under-voltage detection levels                      |

|                      | Under-voltage detection timings (filters, timeouts) |

|                      | - Bus error                                         |

|                      | e.g. pin clamping detection                         |

Table 2: Modelling requirements for different functionalities

The simulation of the GND offset, also refered to as Ground shift, must be possible in the following two ways:

static Ground shift in the range of  $U_{\text{static\_ground\_shift}}$  from -5V to 5V

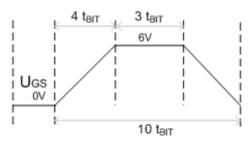

- dynamic Ground shift, see Figure 1 below. ( $t_{Bit} = 2\mu s$ )

Figure 1: Dynamic Ground shift sequence

**Further Implementation Notes**

- Additional Functionalities of a System Basis Chip:

- The functions, relevant for the behaviour at the bus, have to be implemented. This requires the implementation of all bus-sided pins (e.g. CANH, CANL, Split), pins to control and receive the bus signals (e.g. RxD, TxD), power supply pins (e.g. V<sub>SUP</sub>, GND), pins used to signal bus errors and to control the transceiver modes.

- Power dissipation of the bus driver during dominant, recessive or several other operational states shall be reflected by the current of the V<sub>CC</sub> (V<sub>BAT</sub>) pin. The transition implementations may be simplified.

#### 3.5 Model Parameterisation

A transceiver simulation model shall support three different operating areas selected by the model parameters "Typical", "High\_Temp", "Low\_Temp" including the  $V_{CC}$  influence.

- In the operating area "Typical", the typical transceiver behaviour at room temperature shall be provided, similar to the typical data defined in the product data sheet.

- In the operating area "High\_Temp", the corner case behaviour of a worst-case transceiver corresponding to a high environmental temperature condition shall be provided. This corner case shall reflect the corresponding worst-case transceiver parameters reflected by the min/max definitions in the product data sheet, which are reached at high temperatures like e.g. the highest loop delay or weakest driver strength (direction of temperature influence depends on implementation and technology).

- In the operating area "Low\_Temp", the corner case behaviour of a worst-case transceiver corresponding to a low environmental temperature condition shall be provided. This corner case shall reflect the corresponding worst-case transceiver parameters reflected by the min/max definition in the product data sheet, which are reached at low temperatures like e.g. the shortest loop delay or highest driver strength (direction of influence depends on implementation and technology).

Goal of the corner case models is allowing to simulate a worst-case system, which might exist in a vehicle combining multiple transceivers including all silicon production spread and temperature influences.

Within these parameter sets not only parameters based on technology:

- resistance load,

- capacitance load

have to be considered but also the influences of operation parameters:

- specified supply voltage limitations,

- specified limitations of temperature.

In this context, the following transceiver properties have to be implemented in such a way that they can be parameterized within the range of valid transceiver values:

- rise time and fall time of the bus signals (e.g. CANH, CANL),

- Propagation delay (e.g. TxD → CANH / CANL, CANH / CANL → RxD),

- Properties of the transmitter (e.g. R<sub>on</sub>, signal symmetry, current drive capability),

- Properties of the receiver (e.g. R<sub>CM</sub>, receiver thresholds, hysteresis).

## 3.5.1 Implementation

Due to the physical dependencies, it is possibly unrealistic to vary the above mentioned parameters separately or directly. Therefore the quantities, that have any influences on these parameters, may be parameterized instead (e.g. temperature operating mode,  $V_{CC}$  operating mode: see 3.3 and 3.5).

Accordingly, additional pins or parameters are to be used, which allow the variation of the models. In this way the above mentioned transceiver properties (e.g. propagation delay, impedances) are indirectly variable. The aim is to obtain a realistic transceiver behaviour, in order to simulate the influence of these variances in the network. Within the model, the parameters shall be tested for their range of valid values and the adjustable range. The parameter dependency shall be documented (see Ch. 4.1).

To handle different models from different manufacturers in one topology correctly, these have to be optimised for only one simulation algorithm (Newton-Raphson) and a fixed time stepping to avoid or at least limit the different model and simulation behaviour at different simulator tools and thus, increase the reproducability of the model test.

Remark: The Newton algorithm was selected to ensure exchangeability of models in a mixed simulation.

## 3.6 Levels of model implementation

Depending on the functionality and interfaces supported by the model, three different levels of model implementation can be distinguished. The level 1 model is considered to enable first bus signal integrity checks at an early point of time. Level 2 and 3 models cover higher functionality. An analogue implementation is required for all modeled pins, unless this will be contradicted by one of notes below. The greyed pins at the figures in the table below for level 1 and level 2 are considered to be optional regarding their presense at the real device. (6)

|               | Level 1              | Level 2                                          | Level 3                                       |

|---------------|----------------------|--------------------------------------------------|-----------------------------------------------|

| Use Cases     | Bus signal integrity | Bus signal integrity                             | Bus signal integrity                          |

|               |                      | <ul> <li>Network power-up/down</li> </ul>        | <ul> <li>Network power-up/down</li> </ul>     |

|               |                      | - Diagnosis (4)                                  | - Diagnosis                                   |

| Functionality | Transmitter function | Transmitter function                             | <ul> <li>complete functionality as</li> </ul> |

|               | Receiver function    | <ul> <li>Receiver function</li> </ul>            | specified in data sheet                       |

|               | - Bus biasing        | - Bus biasing                                    |                                               |

|               |                      | - Operating modes (5)                            |                                               |

|               |                      | - Bus wake-up (5)                                |                                               |

|               |                      | Local wake-up (5)                                |                                               |

| Interfaces    | - CC interface (1)   | - CC interface                                   | <ul> <li>all pins of device</li> </ul>        |

|               | - Bus interface (3)  | - Bus interface (3)                              |                                               |

|               | Supply interface     | <ul> <li>Supply interface</li> </ul>             |                                               |

|               |                      | Host control interface (2)                       |                                               |

|               |                      | Voltage regulator                                |                                               |

| Pin-out       | ρ                    | <b>Ο Ο Ο</b>                                     | Device specific                               |

|               | V <sub>CC</sub>      | V <sub>IO</sub> V <sub>CC</sub> V <sub>BAT</sub> |                                               |

|               | V <sub>CC</sub>      | V <sub>IO</sub> V <sub>CC</sub> V <sub>BAT</sub> |                                               |

|               | O— TxD GND —O        | O— TxD GND —O                                    |                                               |

|               | O—RxD CANH—O         | O—RXD CANH—O                                     |                                               |

|               | CANL —O              | O—OPMO CANL —O                                   |                                               |

|               | SPLIT —O             | O                                                |                                               |

|               |                      | O—WAKE SPLIT —O                                  |                                               |

| 1             |                      |                                                  |                                               |

|               |                      |                                                  |                                               |

Table 3: Levels of model implementation

### Notes:

- (1) The CC interface of a level 1 model can be implemented digital or analogue.

- (2) The host control interface for a level 2 model shall be implemented by dedicated control pins OPM0 and OPM1, regardless of the actual implementation of the silicon device. The use of the pins shall be documented.

- (3) The SPLIT pin of the bus interface for a level 1 or 2 model shall only be modelled when the real device contains a split pin, too.

- (4) At level 2, only the Diagnosis capabilities regarding the undervoltage detection threshold levels and timings shall be implemented.

- (5) The Functionalities for operating modes, bus- and local wake-up shall only be implemented if the real device contains the specific pins, too.

- (6) The scope of the simulation models is the signal integrity (cp. chapter 1.2). For that reason, the implementation of the models shall concentrate to the described functionality, interfaces and pin-out (cp. table 3). I.e. that e.g. an integrated Vcc regulator of a not stand alone transceiver like SBC does not have to be modelled, but his influence to the transmitter unit has to be considered. In case that an integrated Vcc regulator is not implemented, the parameters like current consumption can not be accurately reflected versus device specification. This and all other deviations of the model from the real device should be mentioned in the model documentation.

Since the different bus driver types partially show significant differences regarding function, options and modes, subsequently the basic scope is described. Therefore the control pins to set the operating modes of a device are named in a general way with OPM0 and OPM1. No SPI Interface capabilities are required to be implemented with these control pins nor any other pin. Additional specific model requirements shall be decided by the GIFT consortium and shall be described in a separate functional requirements document. the contact persons are listed in chapter 5.

# 4 Support Requirements

With the creation and delivery of transceiver models, the following chapters define support services that are expected from the semiconductor manufacturer.

#### 4.1 Model Documentation

A detailed description of the following items has to be provided:

- the implemented transceiver functionalities and properties

- the functions and the simplifications that are not implemented

- parameters and interfaces (functions, behaviour, default value, type):

e.g. pin name, pin type, signal name, signal type, parameter name, parameter type, quantity name, quantity type

- important internal values of the model (e.g. internal states)

- important physical values that are modelled and observable

- range of validity (of signals, pins, quantities, parameters)

- the model parameterization of the desired variable properties and their effect according to chapter 3.5,

documentation of possible parameter settings and their consequence in a spreadsheet

- implementation of error and warning reports

- integration of the model into test bench

- supported analysis types

- recommended simulator settings / initial values (for iteration / convergence)

- test report of the entire model

- known deviations of the model to the real transceiver

- used version of the IEEE standard of VHDL-AMS

## 4.2 Model Application

- Generation and description of a symbol suitable to the model

- Pin names of the model shall match to the datasheet specifications

- Preparation of example simulation project(s)

- If necessary, support on model application / model integration

- Initial verification of the models with the transceiver and documentation of relevant deviations within a defined test bench

- Determination of the simulation speed of the transceiver models using a defined test bench

#### 4.2.1 Test Bench

Test bench will be defined in a separate document. The signals shall be simulated in the test bench using the different parameter sets and shall be measured in a real test bench setup. The simulated curve progressions represents the limits for the measured curves.

## 4.3 Model Maintenance

- Modification of the model due to model errors

- model update including the documentation in the case of product changes

- description of version and model differences

- contact for model maintenance and use

# 4.4 Delivery Dates

- The delivery date will be coordinated with the GIFT Consortium (e.g. transceiver model delivery together with delivery of transceiver samples)

- Coordination with the GIFT Consortium about a possible step-wise implementation of the models

# 5 Contacts

C&S Group GmbH Topology Quality Assurance

Am Exer 19c D-38302 Wolfenbuettel Phone: +49 5331 90555 - 0 Fax: +49 5331 90555 - 110

eMail: topqa@cs-group.de www.cs-group.de

## 6 Annex

# 6.1 Handling of uncovered models

Models older than the release date of the version 1.0 of this specification or models not based on any version of this specification and models not covering the latest version of this specification shall be delivered with a denotation, into which level of model implementation at each version of this specification they refer to best.

16